|

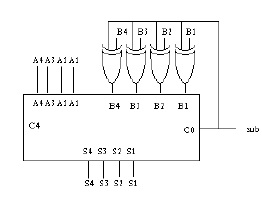

It is the main component inside an ALU of a processor and is used to increment addresses, table indices, buffer pointers, and other places where addition is required. This is code is for an simple asynchronous wrapping n-bit adder. Verilog Code for Full Adder using two Half adders - Structural level Full adder is a basic combinational circuit which is extensively used in many designs. Use full adder step-by-step for bit pairs, so when finish last step, we have final result.

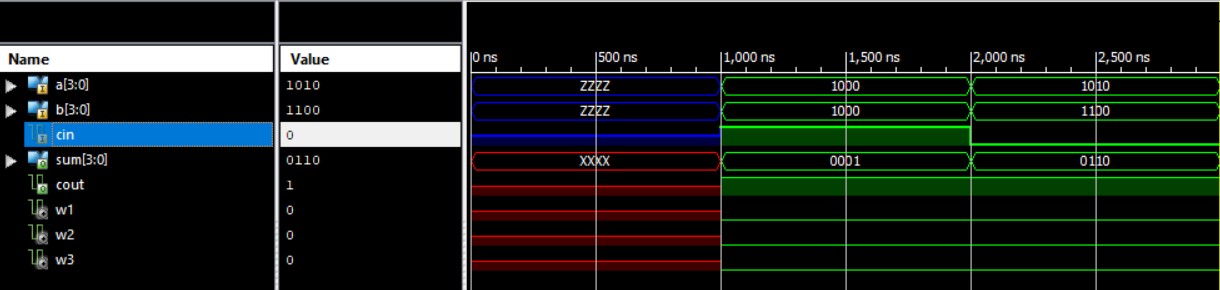

a & b are the number inputs and cIn is the carry input. The full adder is a digital component that performs three numbers an implemented using the logic gates.

A Verilog code for the full adder of four bits which accepts the two inputs 'a' and 'b' each is of 4-bits length. The following individual components have been modeled and have been provided with their corresponding test benches: Parrallel Input Serial Output Shift register (PISO) (piso.v) D Flip Flop (d_flipflop.v) Full Adder (full_adder.v) Verilog Code For Half Adder and Full Adder : Half Adder Using Data Flow: module ha ( a, b, s, c) input a, b out. JanuJanuVB code, verilog adder, behavioral, gates, half adder.

We identified it from trustworthy source. JanuJanuVB code, verilog adder, full adder, half adder A full adder using two half adders is implemented here. In this we are going to share the Verilog code of carry save adder.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed